Project

Repository..!!

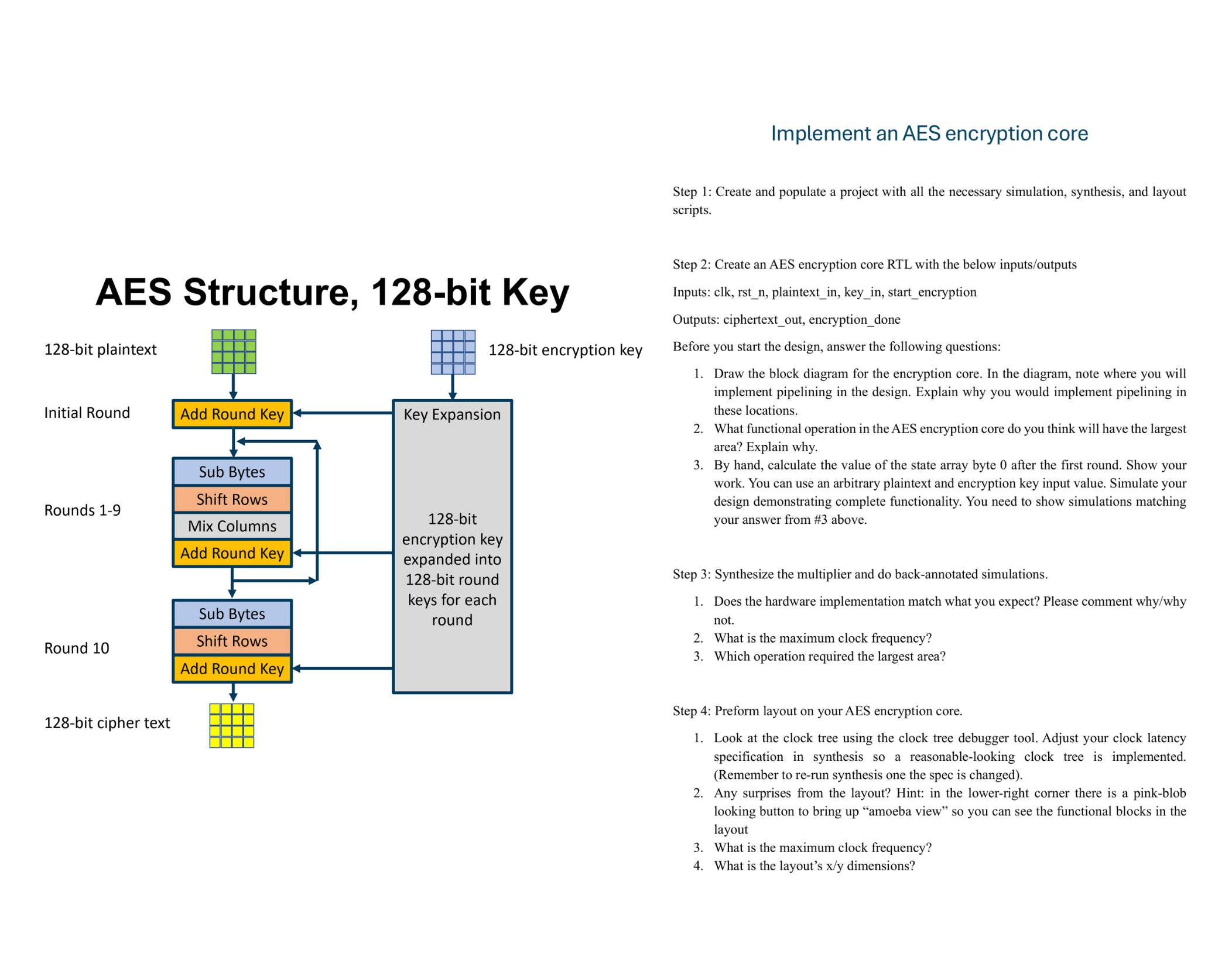

- Designed and implemented an AES-128 encryption core in Verilog, utilizing a 10-round pipelined architecture with SubBytes, ShiftRows, MixColumns, and AddRoundKey transformations for high-throughput encryption.

- Optimized FPGA resource utilization through register retiming and logic balancing, improving area and power efficiency.

- Performed synthesis, back-annotation, and layout analysis, generating STA reports for timing closure, area, and clock performance.

- Verified the design using Tmax ATPG for fault coverage analysis, conducted functional and gate-level simulations, and generated coverage reports to validate correctness.

- Designed and implemented an AES-128 encryption core in Verilog, utilizing a 10-round pipelined architecture with SubBytes, ShiftRows, MixColumns, and AddRoundKey transformations for high-throughput encryption.

- Optimized FPGA resource utilization through register retiming and logic balancing, improving area and power efficiency.

- Performed synthesis, back-annotation, and layout analysis, generating STA reports for timing closure, area, and clock performance.

- Verified the design using Tmax ATPG for fault coverage analysis, conducted functional and gate-level simulations, and generated coverage reports to validate correctness.

- Designed and implemented an AES-128 encryption core in Verilog, utilizing a 10-round pipelined architecture with SubBytes, ShiftRows, MixColumns, and AddRoundKey transformations for high-throughput encryption.

- Optimized FPGA resource utilization through register retiming and logic balancing, improving area and power efficiency.

- Performed synthesis, back-annotation, and layout analysis, generating STA reports for timing closure, area, and clock performance.

- Verified the design using Tmax ATPG for fault coverage analysis, conducted functional and gate-level simulations, and generated coverage reports to validate correctness.

- Designed and implemented an AES-128 encryption core in Verilog, utilizing a 10-round pipelined architecture with SubBytes, ShiftRows, MixColumns, and AddRoundKey transformations for high-throughput encryption.

- Optimized FPGA resource utilization through register retiming and logic balancing, improving area and power efficiency.

- Performed synthesis, back-annotation, and layout analysis, generating STA reports for timing closure, area, and clock performance.

- Verified the design using Tmax ATPG for fault coverage analysis, conducted functional and gate-level simulations, and generated coverage reports to validate correctness.

- Designed and implemented an AES-128 encryption core in Verilog, utilizing a 10-round pipelined architecture with SubBytes, ShiftRows, MixColumns, and AddRoundKey transformations for high-throughput encryption.

- Optimized FPGA resource utilization through register retiming and logic balancing, improving area and power efficiency.

- Performed synthesis, back-annotation, and layout analysis, generating STA reports for timing closure, area, and clock performance.

- Verified the design using Tmax ATPG for fault coverage analysis, conducted functional and gate-level simulations, and generated coverage reports to validate correctness.

- Designed and implemented an AES-128 encryption core in Verilog, utilizing a 10-round pipelined architecture with SubBytes, ShiftRows, MixColumns, and AddRoundKey transformations for high-throughput encryption.

- Optimized FPGA resource utilization through register retiming and logic balancing, improving area and power efficiency.

- Performed synthesis, back-annotation, and layout analysis, generating STA reports for timing closure, area, and clock performance.

- Verified the design using Tmax ATPG for fault coverage analysis, conducted functional and gate-level simulations, and generated coverage reports to validate correctness.

- Designed and implemented an AES-128 encryption core in Verilog, utilizing a 10-round pipelined architecture with SubBytes, ShiftRows, MixColumns, and AddRoundKey transformations for high-throughput encryption.

- Optimized FPGA resource utilization through register retiming and logic balancing, improving area and power efficiency.

- Performed synthesis, back-annotation, and layout analysis, generating STA reports for timing closure, area, and clock performance.

- Verified the design using Tmax ATPG for fault coverage analysis, conducted functional and gate-level simulations, and generated coverage reports to validate correctness.